Risk vs. Uncertainty: Building Resilience into America’s Semiconductor Future

- Alexandria, VA | August 13, 2025

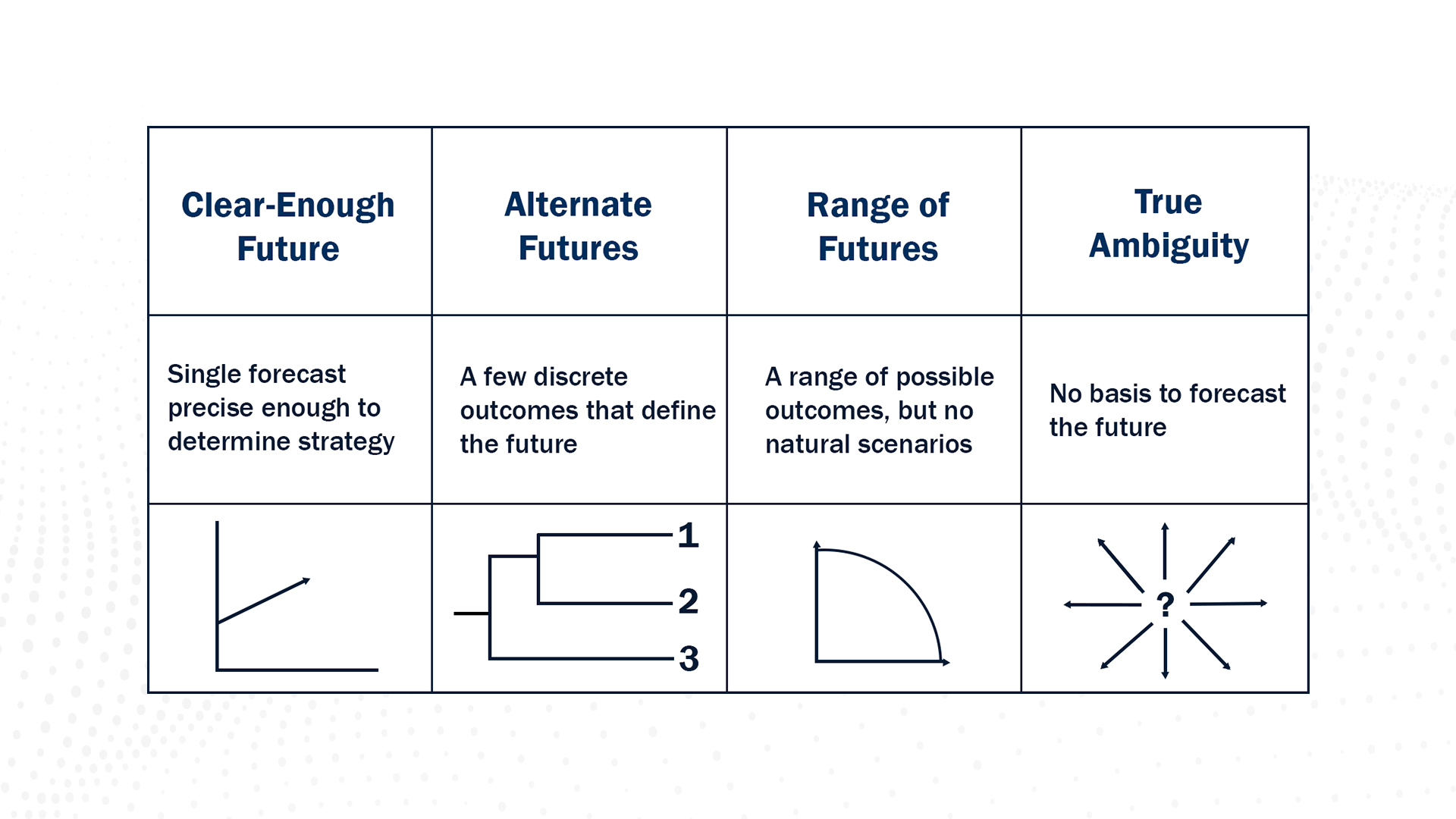

Drawing on research like Harvard Business School’s Strategy Under Uncertainty, Cabaniss emphasizes that uncertainty is not just the absence of information. It can range from well-defined potential outcomes to broad ambiguity about future events. The semiconductor industry, given its complexity and exposure to global forces, sits in the middle of the uncertainty spectrum with a broad range of possible outcomes.

“

Mapping supply chains beyond the first tier. Policymakers and defense leaders need better visibility into suppliers three, four, or even five levels deep. These hidden dependencies often cause the biggest problems during disruptions.

Investing in redundancy. Single points of failure must be identified and mitigated, even if doing so comes with upfront costs. This could include diversifying fabrication capabilities geographically or supporting domestic packaging and testing industries.

Embracing scenario planning. Strategy should account for multiple possible futures, not just the most likely one. This includes considering geopolitical flashpoints, cyberattacks, natural disasters, and other threats that could disrupt chip access.

Expanding industry-government collaboration. Neither DoD nor any single tech company can solve this challenge alone. Cross-sector and international partnerships are essential for aligning incentives and building resilience throughout the ecosystem.

- Mapping supply chains beyond the first tier. Policymakers and defense leaders need better visibility into suppliers three, four, or even five levels deep. These hidden dependencies often cause the biggest problems during disruptions.

- Investing in redundancy. Single points of failure must be identified and mitigated, even if doing so comes with upfront costs. This could include diversifying fabrication capabilities geographically or supporting domestic packaging and testing industries.

- Embracing scenario planning. Strategy should account for multiple possible futures, not just the most likely one. This includes considering geopolitical flashpoints, cyberattacks, natural disasters, and other threats that could disrupt chip access.

- Expanding industry-government collaboration. Neither DoD nor any single tech company can solve this challenge alone. Cross-sector and international partnerships are essential for aligning incentives and building resilience throughout the ecosystem.

For foundational context on why semiconductor resilience begins with a broader understanding of the entire production and logistics framework, revisit Part 1 of this series.

If they can, the U.S. can lead not just in chip design or advanced manufacturing but in shaping a global model of semiconductor resilience that protects both economic competitiveness and national defense.

For foundational context on why semiconductor resilience begins with a broader understanding of the entire production and logistics framework, revisit Part 1 of this series.

In Part 3, we examine the physical infrastructure barriers—from permitting delays to power generation limits—that threaten to stall America’s semiconductor ambitions. And in Post 4, we explore how moving from siloed efforts to integrated systems thinking can help align government, industry, and international allies around a more secure and sustainable future.

Subscribe now so you won’t miss a post in this series. We respect your privacy and inbox, sending no more than one email per week.

Related Posts

We invite you to subscribe and stay informed. Never miss an update as we continue providing the rigorous insights and expert analysis you rely upon to protect and advance our national security.